一、USB3.0接口介绍

https://www.usb.org/sites/default/files/CabConn_Legacy_3_1_Compliance_Rev_1_1.pdf

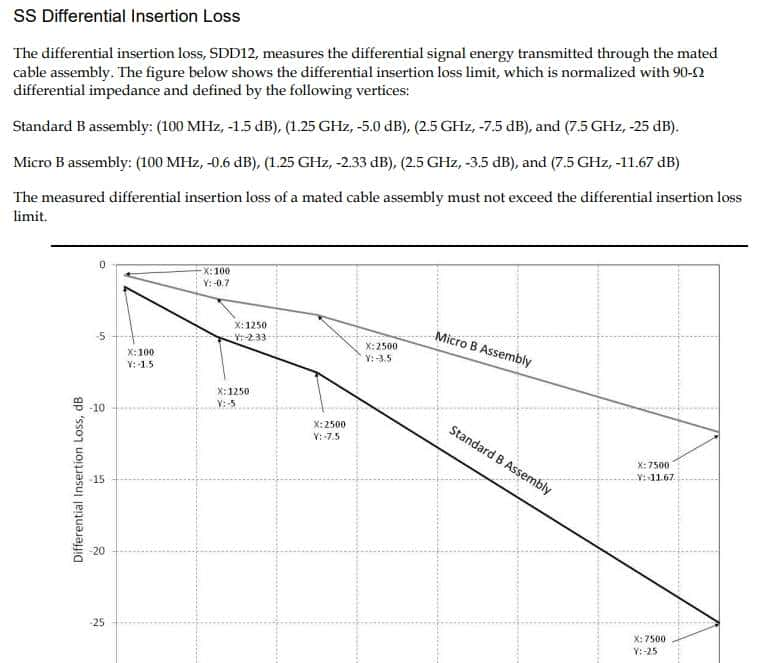

文档里面有关于USb3.0高速接口的要求。对差分对插入损耗的要求:这是对整个USB线路上的插损的要求,包括线缆、连接器、过孔等等

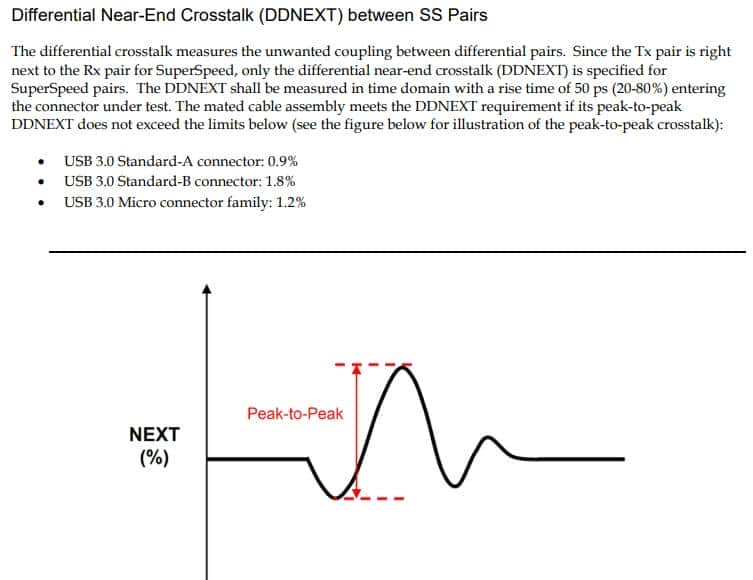

差分对近端串扰的要求:

SS和DP DM之间串扰的要求

模态转换的要求,不超过-20dB

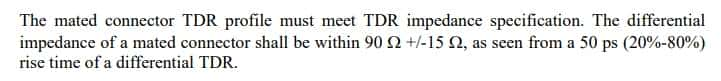

连接器阻抗TDR的要求

这次主要就是仿真TDR的变化来优化设计。

TDR是什么意思?

TDR是多个英文单词的缩写,包括:Time-Domain Reflectometry—时域反射技术,一种对反射波进行分析的遥控测量技术,在遥控位置掌握被测量物件的状况;此外,还有,time domain reflectometry(时-空反射测量);time-delay relay (时延继电器);transmit data register(发送数据寄存器)等。

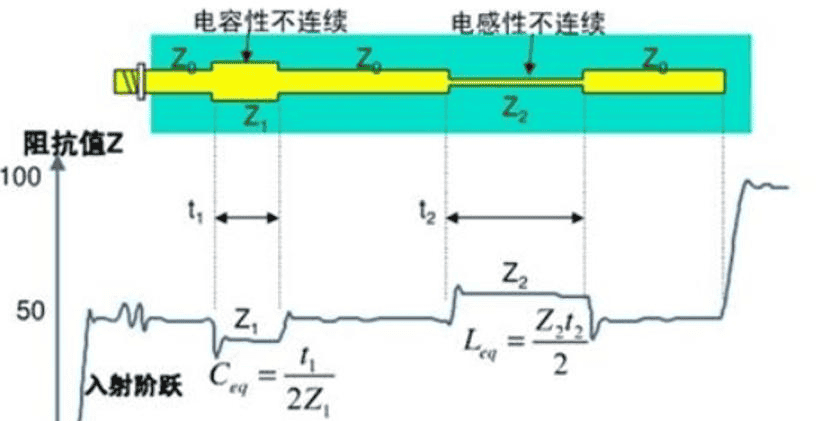

TDR (Time Domain Reflectometry)时域反射技术的原理(TDR测量原理)是,信号在某一传输路径传输,当传输路径中发生阻抗变化时,一部分信号会被反射,另一部分信号会继续沿传输路径传输。TDR是通过测量反射波的电压幅度,从而计算出阻抗的变化;同时,只要测量出反射点到信号输出点的时间值,就可以计算出传输路径中阻抗变化点的位置。

TDR时域反射计向被测电缆发送一个低压脉冲,并且在电缆内阻抗变化的情况下,都会看到反射。TDR时域反射计TDR测试从反射释放到低压脉冲释放之间的时间。通过测量时间并知道脉冲的传播速度,便可以计算到反射的距离,从而得出电缆长度或者故障点距离。还可根据不同的发射波形判断电缆中可能出现的阻抗变化或故障类型的信息。

二、USB信息

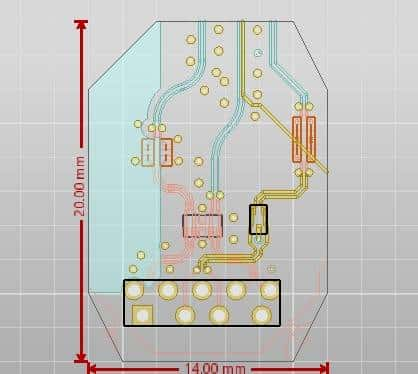

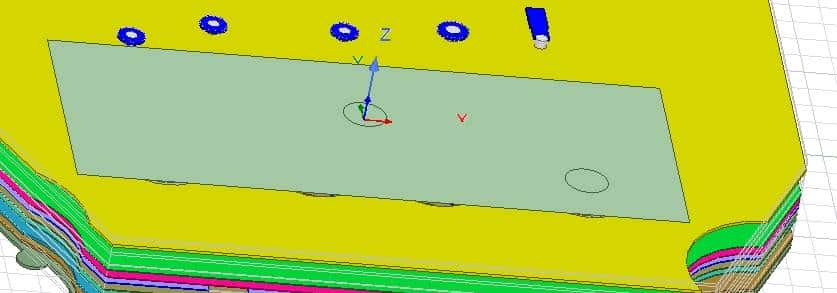

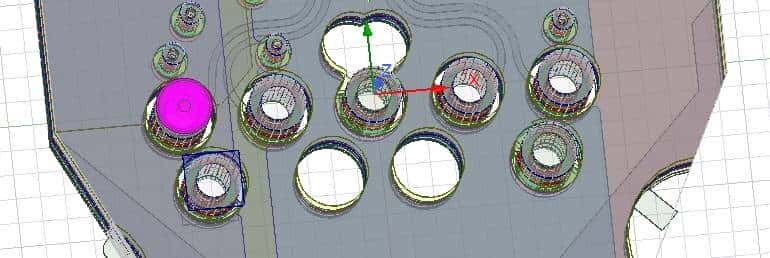

在PCB上的位置

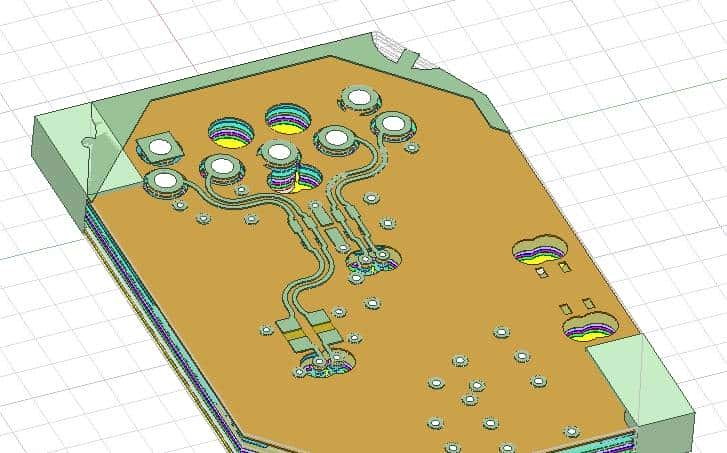

在底层经过ESD,RX经过ESD到第三层,然后进入CPU;TX端还经过了交流耦合电容。

需要关注连接器、ESD、交流耦合电容、过孔等造成的阻抗不连续。

对于CPU这一侧,使用的是盲孔,1-3层,这种孔结构非常短,12mil左右,它对阻抗不连续造成的影响非常小,小到可以忽略。这里需要关注它的回流。它到第二层3.9mil、到第五层11.3mil,所以它的回流主要在第二层。这里第三层附近有过孔连到第一层回到CPU的地引脚,第五层也有,没问题。

能否满足要求主要看连接器那端了。

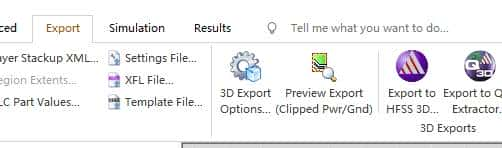

USB接口那端的优化主要是结构方面的,使用HFSS打开提取S参数,再去算TDR。

三、HFSS提取S参数

Allegro导出ODB++

Next-Close完成。

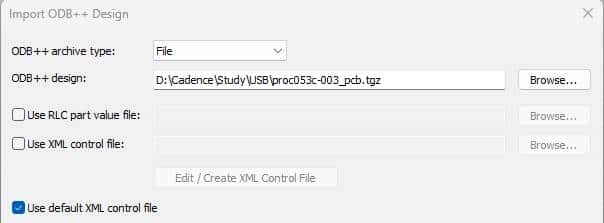

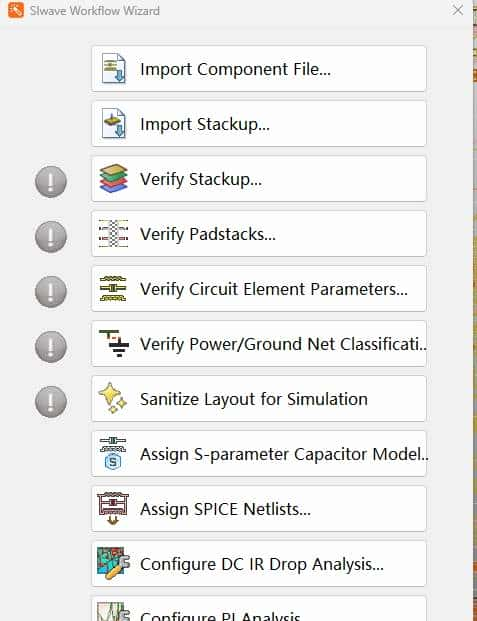

打开Ansys SIwave,导入ODB++

选择刚才导出的那个文件

Import

Import Configuration

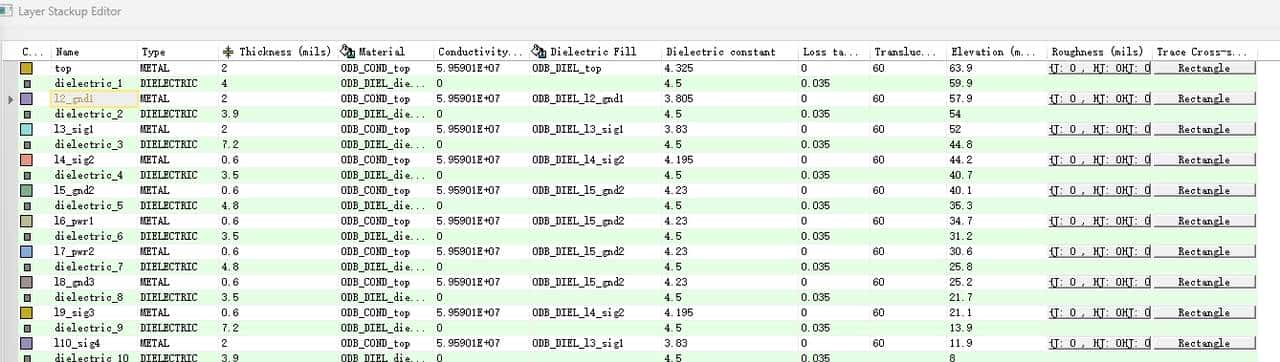

X掉,保存。检查层叠结构,转换过程大概率结构会变。改回自己的层叠结构的每一层的厚度值。还有就是介电常数。铜导体层也有介电常数,它指的是导体层的金属被腐蚀掉的挖空部分的填充介质的介电常数。这里是随便找的板子,不知道确切的介电常数,就按默认值了。

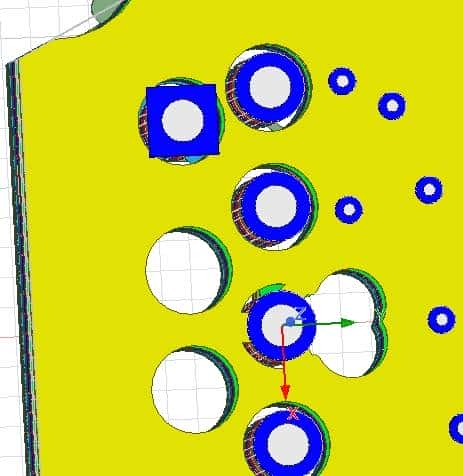

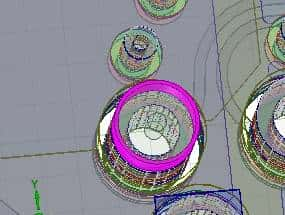

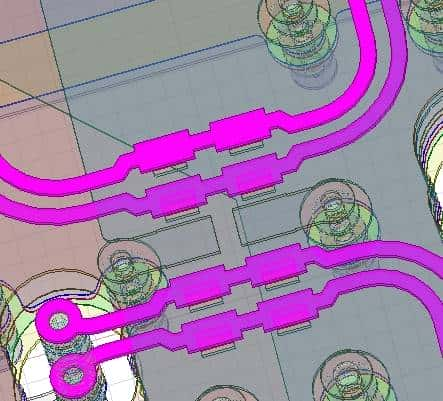

然后就是把USB端口附近的结构给切出来,切的时候注意需要测量的信号应该有个水平或垂直的切面,否则后期在HFSS里面不好添加端口。

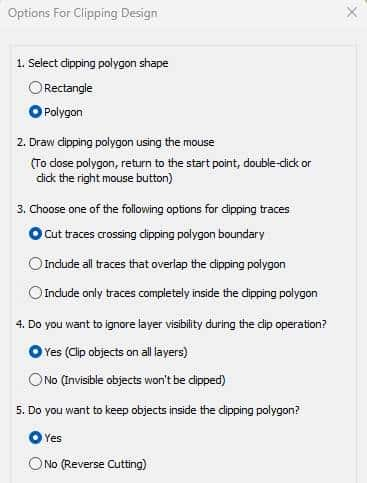

菜单Tools->Clip design 用个多边形的 切的边沿到仿真的信号至少留5倍线宽的距离,方便加波端口。

点击、画线,把要切的结构包含进去,关键信号留足间距

点clip,切,保存一下

检查一下层叠结构、不要出错了

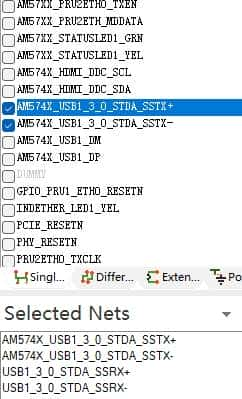

选择需要导出的信号

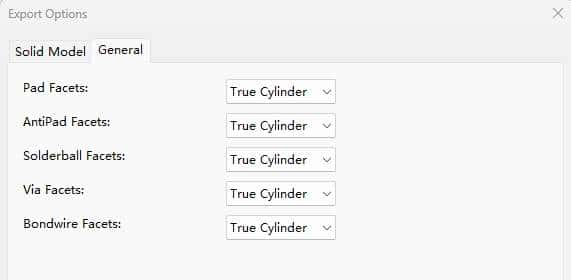

然后设置导出选项,导出到HFSS里面。选项里Generate fully unified nets,是要相同网络的结构弄成一个整体结构,不要勾选;Square off trace ends,导线截面是方形,需要勾选,不然没法加端口;general里面是用几边形替代圆柱的形状,这里就用真正的圆柱形。

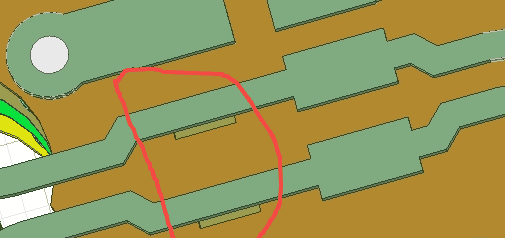

这里DP、DM因为导出时没有包含,形成的挖空区,实际应该包含,因为离信号比较近而且挖空面积较大,对信号是有影响的。

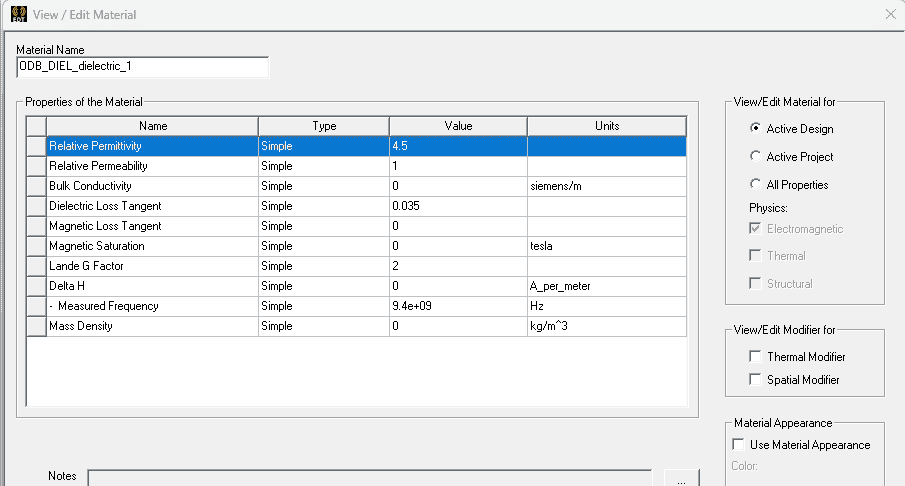

修改介电常数

点击View/Edit Materials…需要用频变介电常数

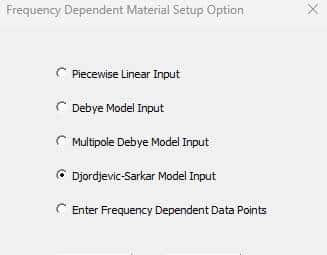

Set Frequency Dependency…

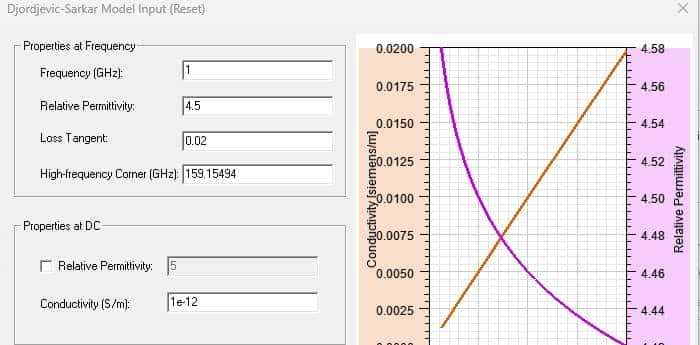

选择DS模型

这里随便设置,实际需要根据自己使用的材料设置。

其它的也类似设置。

把导体部分材料设置为copper。

把自动生成的空气盒子删除。

设置坐标,Modeler-Coordinate System-Create-Relative CS-Offset,把原点设置在USB接插件的中间的引脚上,方便以后设置。

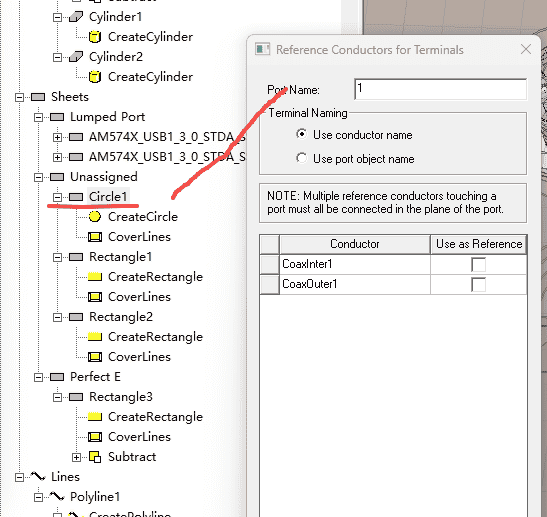

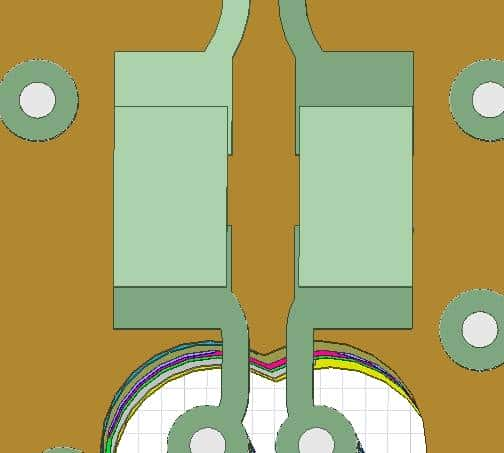

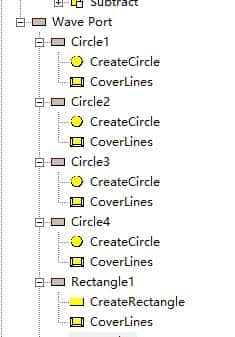

添加端口

波端口,上边接触到上参考平面的下边沿,下边接触到下参考平面的上边沿。左右延申5倍线宽,线宽4.3mil

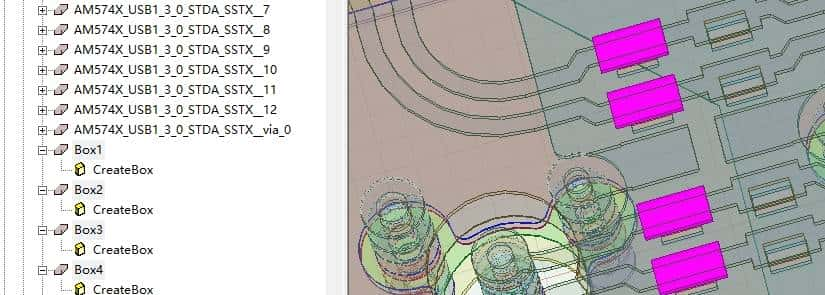

接插件这一侧,使用同轴端口:在USB接插件地引脚上添加圆柱导体,高度设置为铜皮厚度的2倍就行了,铜皮是2mil,这里设置为4mil。直径与孔的直径一致就行了。

添加理想电平面,贴在刚才的两个铜柱之上,覆盖接插件所有引脚。

把两个铜柱设置为理想电导体pec,添加的这个平面设置为理想电边界Perfect E。

设置同轴线输入的电芯,就是一个柱子,贴在信号引脚上,高度超过刚才理想电边界5倍的第一个介质层的厚度,第一个介质层厚度是4mil,5倍是20mil,加上刚才的4mil高度,总共24mil,直径设置为7mil,材料还是pec。

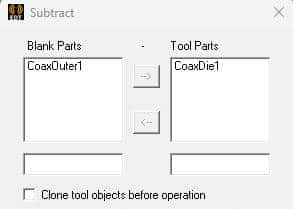

做同轴线的屏蔽层,也是一个圆柱,直径与孔外径相同,23mil,高度从理想电边界的4mil位置到电芯的高度24mil。理想电边界不能跟同轴线的芯连接,这里选中理想电边界和同轴线的屏蔽层,两者进行Subtract运算。勾选拷贝。

添加同轴线的介质

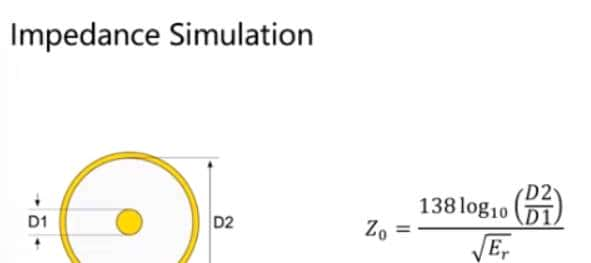

同轴线需要是50欧的,计算公式是:

刚才同轴线,芯直径D1,7mil,D2是21,计算得到介电常数是1.7。这里直径半径用的混乱,只是仿真步骤记录。

现在外屏蔽层、介质都是实心的,运算一下:外屏蔽层-介质

介质和内部同轴线芯也是重叠的,但是计算的时候,软件会自动处理,可以不用管了。

同轴端口设置:在同轴线的顶面画一个圆,半径与屏蔽层的最外圈一致就行了,23mil。

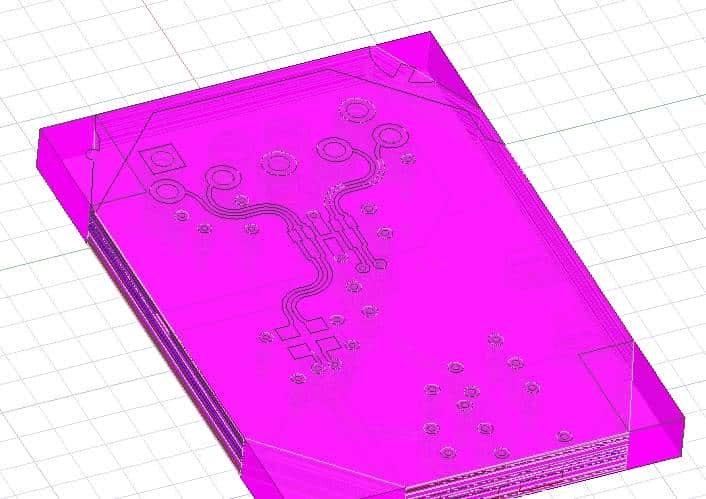

画空气盒子:空气盒子需要贴边,暂时补上对角的两个缺角,再画空气盒子。补全的目的是为了画空气盒子的时候找坐标。

然后删除刚才的那两个补角的。

空气盒子的材料,air,高度设置一下,上边沿与刚才的同轴线的上边沿对齐,向下也要高出5倍介质厚度,可以弄成对称的,上下各延伸24mil。透明度设置100%。

端口设置。

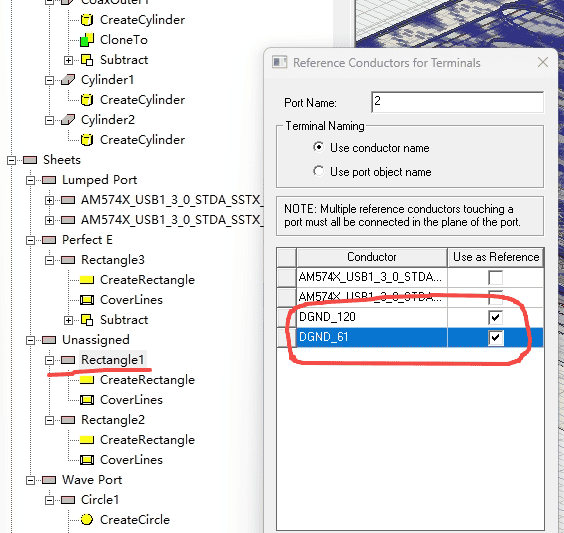

点同轴端口,右键–激励–WavePort,参考地选择外边的屏蔽层CoaxOuter1。

之前的矩形信号截面,也要设置波端口,参考平面包括上下两个地平面。

还有个问题,ESD器件在导出结构的时候,丢了一排焊盘

这个地方下面有挖空,不补齐会有阻抗不连续点,仿真结果不正确。按照旁边的焊盘画一个同样大小的box,材料为铜,跟导线unite在一起。

交流耦合电容两端也要用铜导线连接起来。贴在两个焊盘上画铜皮,厚度1mil就可以了。

到这里,还缺三个同轴端口,补上。

空气盒子设置辐射边界。右键–assign boundary–Radiation…就是让电磁波到达边界后出去,而不是反射回来形成振荡。

仿真设置

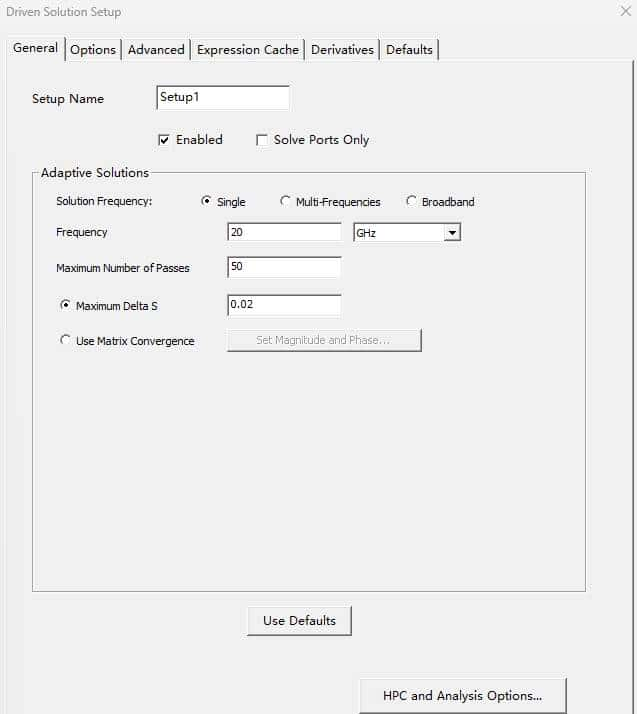

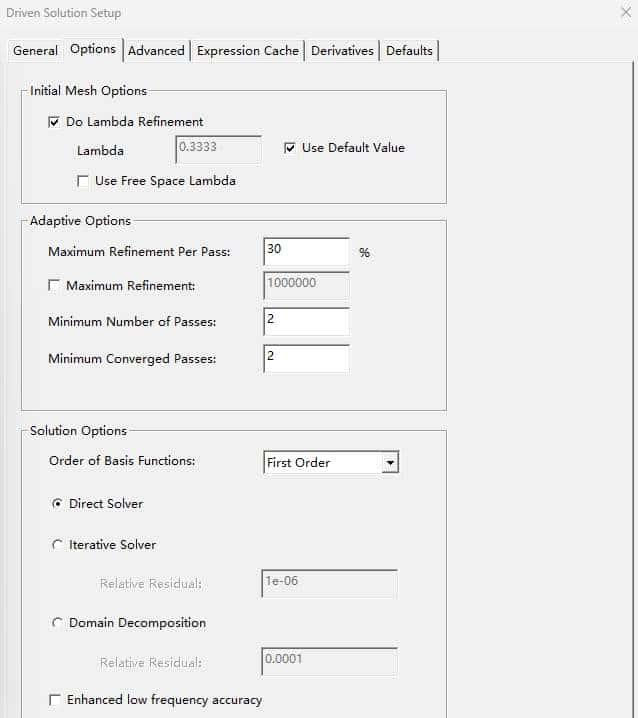

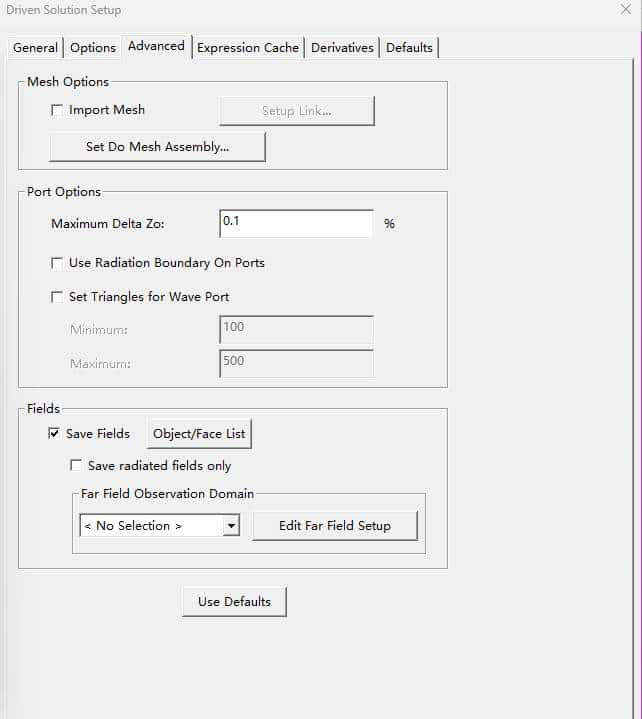

求解频率,协议里要求上升时间50ps,也就是10G,这里仿真到20G;迭代次数设置大一些,保证收敛;Delta S越小划分网格越多,计算量越大,根据电脑配置还有需要的精度来估计一个;Options里面,连续达标几次才算收敛成功,2;Advanced里面,端口delta Z,设置稍小一些。

设置扫频

Analyze All仿真

时间比较长。

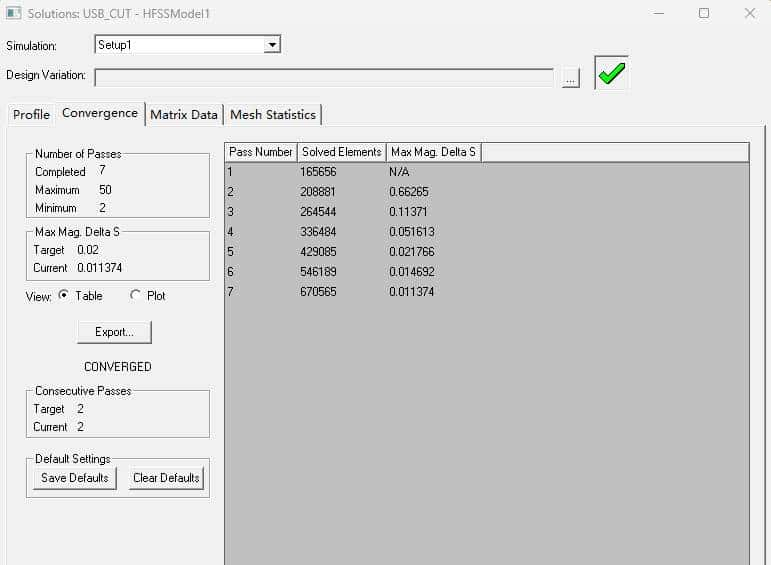

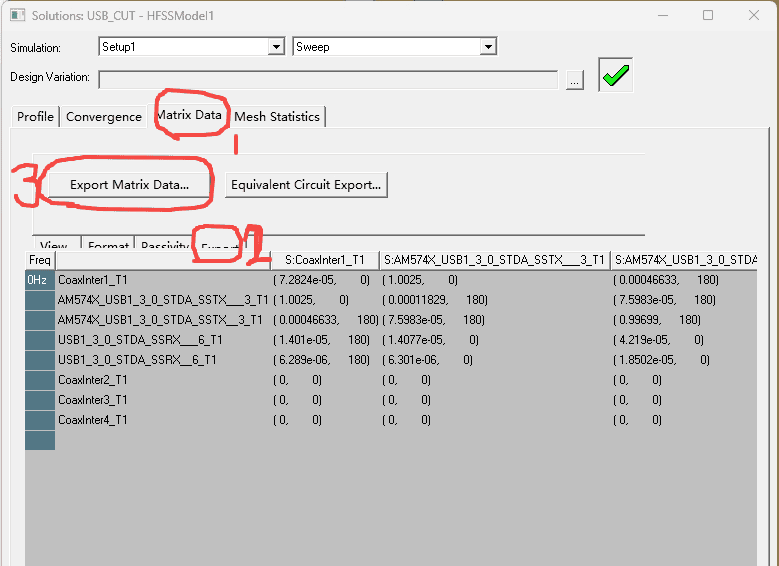

仿真结束之后,查看仿真是否成功,这里可以看到第七次就成功了,计算量67万;成功后把它的S参数导出来

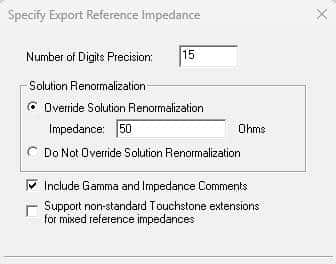

导出的参数设置,第一个是精度推荐6-9位小数就可以了,太大的话文件会很大而且对计算结果的准确度没有明显提升;第二个是归一化阻抗到50欧姆

暂停,有空了再继续。

相关文章