目录

第一章:存储技术演进与NVMe的崛起

1.1 从HDD到SSD:存储介质的革命

1.2 接口瓶颈:为何SATA与SAS不再适合高速闪存?

1.3 NVMe的诞生:为闪存而生的高效协议

1.4 NVMe over Fabrics的扩展:打破机箱界限

第二章:PCI Express基础与NVMe的基石作用

2.1 PCIe总线架构深入解读:拓扑、分层与数据包

拓扑结构

分层模型

数据包类型

2.2 PCIe配置空间:如何被发现与识别?

2.3 PCIe数据传输机制:TLP、DLLP与流控

TLP详解

流量控制

2.4 MSI/MSI-X中断机制:高性能中断的保障

2.5 NVMe如何构建在PCIe之上:一个高效的“乘客”

第三章:NVMe 1.4c规范精解(上) – 命令与队列

3.1 基本概念:控制器、命名空间、队列

3.2 提交队列与完成队列:生产者-消费者模型的完美体现

3.3 门铃寄存器:高效的硬件信令机制

3.4 Admin队列与I/O队列:管理平面与数据平面的分离

3.5 NVMe命令格式详解:PRP与SGL两种数据指针

PRP

SGL

3.6 命令执行的全流程:从驱动到硬件的旅程

3.7 多队列与多核心扩展性:为何NVMe能充分利用CPU?

队列分配策略

性能优势体现

3.8 端到端数据保护:DIF/DIX详解

保护信息格式

保护类型

3.9 命名空间管理、附件与分区

命名空间管理

命名空间附件

分区命名空间

3.10 持久化日志区域与异常恢复

持久化事件日志

异常恢复流程

3.11 Sanitize、Firmware管理等高阶功能

Sanitize操作

固件管理

其他高级特性

3.12 NVMe over Fabrics初探

基本架构

主要传输类型

核心价值

本章总结

第四章:NVMe协议扩展与系统集成

4.1 多路径I/O与命名空间共享

多路径I/O架构

实现机制

4.2 虚拟化支持:SR-IOV与MR-IOV

SR-IOV架构

关键特性

MR-IOV进阶

4.3 电源管理:自动功耗状态转换

功耗状态

自动状态转换

4.4 温度管理与热节流

温度监控

热节流策略

主动冷却集成

4.5 时间命名空间与确定性延迟

确定性延迟技术

应用场景

4.6 NVMe与计算存储集成

计算存储架构

计算存储用例

4.7 协议兼容性与多代支持

版本兼容策略

多代设备管理

生态系统影响

本章总结

第一章:存储技术演进与NVMe的崛起

1.1 从HDD到SSD:存储介质的革命

在数字世界的底层,存储系统的演进是一部持续追求速度、容量与可靠性的史诗。要理解NVMe为何是革命性的,我们必须从它的前辈开始讲起。

机械硬盘(HDD) 是统治了数字存储半个多世纪的技术。其工作原理是电磁感应(如图1-1所示)。数据存储在以每分钟5400或7200转高速旋转的磁性盘片上,读写磁头悬浮在盘片上方纳米级的高度,通过磁化盘片上的微小区域来记录数据(写),或通过感应磁场变化来读取数据。

图1-1:机械硬盘(HDD)结构示意图

+-------------------------------------------------+

| HDD 结构 |

+-------------------------------------------------+

| |

| +-----------------------------------------+ |

| | 磁性盘片 | |

| | (多个盘片叠放,双面可记录) | |

| +-----------------------------------------+ |

| ^ |

| | |

| +------v------+ |

| | 读写磁头 |<---(安装在磁头臂上) |

| +-------------+ |

| | |

| +------v------+ |

| | 音圈电机 |(驱动磁头臂径向移动) |

| +-------------+ |

| |

+-------------------------------------------------+

(图例说明: 展示了HDD的核心组件:盘片、磁头、磁头臂和驱动电机。)

HDD的访问过程充满了物理运动:首先,磁头必须移动到目标数据所在的磁道(寻道时间),然后等待盘片旋转到数据所在的扇区下方(旋转延迟),最后才是数据传输。这个机械过程决定了HDD的随机访问延迟通常在毫秒(ms) 级别。这就像在图书馆里找一本书,你需要先走到正确的书架(寻道),然后等旋转的书架把你要的书转到面前(旋转延迟),最后才能阅读(数据传输)。

表1-1:HDD与SSD关键技术特性对比

| 特性指标 | 机械硬盘 (HDD) | 固态硬盘 (SSD) |

|---|---|---|

| 核心原理 | 电磁感应、机械运动 | 半导体电路、电子迁移 |

| 核心组件 | 盘片、磁头、马达 | NAND Flash芯片、控制器、DRAM缓存 |

| 访问延迟 | 毫秒 (ms) 级别 | 微秒 (μs) 级别 |

| 随机I/O性能 | 低 (几十到上百IOPS) | 极高 (数万至数十万IOPS) |

| 功耗 | 较高 (启动和寻道时尤甚) | 较低 |

| 抗震性 | 差 (运动部件易受损) | 强 (全固态结构) |

| 噪音 | 有 (马达和磁头声音) | 无 |

| 单位容量成本 | 低 | 高 |

固态硬盘(SSD) 的到来,终结了机械运动带来的性能瓶颈。SSD基于半导体技术,使用一种名为NAND Flash的存储芯片来持久化数据。数据的读写通过电子的迁移完成,完全没有机械部件。因此,其访问延迟骤降至微秒(μs) 级别,比HDD快了100倍以上。

【实践案例一:延迟的直观感受】

想象一下,如果HDD访问数据所需的时间是1秒钟(一次心跳),那么SSD完成同样操作的时间还不到0.01秒(一次眨眼的时间都不到)。这种速度的代差,是后续一切变革的基础。

1.2 接口瓶颈:为何SATA与SAS不再适合高速闪存?

尽管存储介质已经从HDD升级到了SSD,但计算机系统的其他部分,尤其是连接存储设备的接口,却一度成为了新的瓶颈。SATA和SAS接口是为HDD时代设计的。

SATA:作为PC和消费级领域的主流接口,其演进从SATA 1.0 (1.5 Gbps) 到SATA 3.0 (6 Gbps)。即使是最快的SATA 3.0,其理论带宽上限也仅为600 MB/s左右。

SAS:主要面向企业级和服务器市场,提供了更高的带宽(SAS 3.0为12 Gbps)和更强的可靠性、可连接性。

然而,问题不仅在于带宽。这些接口的协议栈本身也带来了巨大的开销。无论是SATA还是SAS,其底层都运行AHCI 协议。AHCI设计之初,是为了兼容单队列、高延迟的HDD。

AHCI协议的主要瓶颈:

单命令队列:AHCI只有一个命令队列,深度通常为32。这意味着无论系统有多少个CPU核心,它们发出的存储命令都必须挤在同一个队列中等待处理,无法充分利用多核处理器的并行能力。

高延迟:每次命令执行都需要至少4次CPU中断和上下文切换,这在高速SSD上产生了不可忽视的开销。

协议转换开销:数据在系统内存和SSD之间传输时,需要经过多层协议封装和解封装。

我们可以用一个生动的比喻来理解这个瓶颈:

【通俗比喻一:交通比喻】

SATA/AHCI + SSD:好比将一台法拉利跑车(SSD) 开上一条狭窄多弯的乡村公路(SATA接口),并且遵守一套为马车(HDD) 设计的交通规则(AHCI协议)。跑车的引擎性能被严重浪费了。

NVMe:则是为这台法拉利修建了一条笔直宽阔的高速公路(PCIe总线),并配套了一套高效的交通管理系统(NVMe协议),允许所有车道(CPU核心)同时发车,直达目的地。

当单颗SSD的性能轻易突破SATA 3.0的带宽上限时,接口和协议就成了必须被革新的对象。

1.3 NVMe的诞生:为闪存而生的高效协议

面对SATA/SAS的瓶颈,产业界需要一种新的协议,能够充分发挥闪存介质的潜力,并充分利用现代计算机系统的架构。于是,NVMe 应运而生。

NVMe,全称为 Non-Volatile Memory Express,顾名思义,它是一种用于非易失性存储器(如SSD)的高速 协议。

NVMe的设计哲学是 “从头开始,为闪存和并行性而优化” 。它与AHCI的根本区别如下(如表1-2所示):

表1-2:AHCI与NVMe协议关键特性对比

| 特性 | AHCI (用于SATA) | NVMe (用于PCIe) |

|---|---|---|

| 最大队列数量 | 1个命令队列 | 64K个I/O队列 |

| 每个队列的深度 | 32个命令 | 64K个命令 |

| 队列仲裁机制 | 轮询 (RR) | 多种方式 (RR, 加权RR, 紧急优先) |

| 中断处理 | 单消息中断 (MSI) | 多消息中断 (MSI-X),可定向到不同CPU核心 |

| 协议延迟 | ~6μs (软件栈开销) | ~2.8μs (软件栈开销) |

| 并行性 | 差,单队列 | 极佳,每核心可拥有专用队列 |

| 数据保护 | 可选 | 强制端到端数据保护 (可选功能) |

NVMe的核心优势解读:

极致的并行性:支持高达64K个独立队列,每个队列深度64K。这意味着应用程序、CPU核心甚至线程都可以拥有自己的专用命令队列,彻底消除了锁竞争,完美匹配多核时代。

精简的协议栈:NVMe运行在高效的PCIe之上,协议命令本身非常精简,所需的CPU指令数远少于AHCI,从而显著降低了延迟。

面向SSD的特性:原生支持SSD的并行访问特性(如多通道、多Way),并内置了垃圾回收、损耗均衡等管理功能的提示,使SSD能在更优的状态下工作。

【实践案例二:队列模型的直观对比】

想象一个银行柜台:

AHCI模式:只有一个服务窗口(单队列),所有顾客(CPU核心/线程)排成一列。即使有其他空闲的柜员,他们也必须等着这个唯一的窗口。

NVMe模式:有成千上万个服务窗口(多队列)。每个顾客都可以直接去一个空闲的窗口,或者为不同类型的业务(如存款、取款)设立专用窗口。所有窗口可以同时工作,效率天壤之别。

1.4 NVMe over Fabrics的扩展:打破机箱界限

NVMe的成功并未止步于机箱之内。为了将NVMe的低延迟和高性能优势扩展到整个数据中心网络,NVMe over Fabrics 标准被制定。

NVMe over Fabrics 的核心思想是:将NVMe协议映射到各种高效的网络 fabric 之上,使得远程的NVMe SSD能够像本地盘一样被访问。它实现了 “存储网络化” 和 “存储解耦”。

目前主流的NVMe-of实现包括:

NVMe over RDMA:使用RoCE、iWARP 或 InfiniBand 作为底层传输。RDMA允许数据直接从一台计算机的内存传输到另一台计算机的内存,无需双方操作系统的介入,实现了极低的延迟。

NVMe over TCP:使用标准的以太网TCP/IP协议。虽然性能略低于RDMA方案,但其优势在于兼容现有的数据中心网络基础设施,部署成本低,因此迅速成为主流。

图1-2:NVMe本地与NVMe over Fabrics架构对比

+-------------------+ +-------------------+

| 主机系统 | | 主机系统 |

| | | |

| +-------------+ | | +-------------+ |

| | 应用程序 | | | | 应用程序 | |

| +-------------+ | | +-------------+ |

| | | | | |

| +-------------+ | | +-------------+ |

| | NVMe驱动 | | | | NVMe-of驱动 | |

| +-------------+ | | +-------------+ |

| | | | | |

| +-------------+ | | +-------------+ |

| | PCIe 总线 | | | | 网络协议栈 | |

| +-------------+ | | | (e.g., TCP) | |

| | | | +-------------+ |

| +-------------+ | | | |

| | 本地NVMe SSD| | | +-------------+ |

| +-------------+ | | | 网络接口卡 | |

+-------------------+ | +-------------+ |

+---------|---------+

|

+-------v-------+

| 数据中心网络 |

| (Fabric) |

+-------|-------+

|

+---------v---------+

| 目标存储系统 |

| (提供NVMe SSD服务)|

+-------------------+

(图例说明: 左图为本地NVMe架构,右图为NVMe over Fabrics架构,展示了协议如何通过网络延伸到远端。)

NVMe-of的意义在于,它使得构建高性能、低延迟的存储池 成为可能,为云计算的存储架构和 disaggregated storage(解耦存储)提供了关键技术支撑。

【本章小结】

本章我们回顾了从HDD到SSD的介质革命,揭示了旧有接口和协议(SATA/SAS/AHCI)如何成为性能瓶颈。NVMe作为一种为闪存和现代计算架构量身定制的新协议,以其极致的并行性、低延迟和高效性,彻底释放了SSD的性能潜力。而NVMe over Fabrics则进一步将这一优势从单个服务器扩展至整个数据中心。理解了这一演进历程,我们才能更好地领会后续章节中NVMe协议细节设计的精妙之处,以及其在芯片架构中需要考虑的关键因素。

第二章:PCI Express基础与NVMe的基石作用

2.1 PCIe总线架构深入解读:拓扑、分层与数据包

PCI Express是继PCI和PCI-X之后的新一代高速串行点对点互联标准。理解其架构是理解NVMe高性能根源的关键。

拓扑结构

与PCI/PCI-X的并行总线和共享总线架构不同,PCIe采用了一种点对点 和交换 的拓扑结构(如图2-1所示)。每个设备都通过独立的链路连接到交换机,从而实现并发通信,彻底消除了共享总线带来的带宽争用问题。

图2-1:PCIe拓扑结构示意图

+----------------------+

| CPU / 根复合体 |

| (Root Complex) |

+----------+-----------+

| (x16链路)

+------------v-----------+

| PCIe 交换机 |

| (PCIe Switch) |

+------------+-----------+

|

+-----------------------+-----------------------+

| | |

+------v------+ +------v------+ +------v------+

| NVMe SSD | | GPU | | 网卡 |

| (Endpoint) | | (Endpoint) | | (Endpoint) |

+-------------+ +-------------+ +-------------+

(图例说明: 展示了典型的PCIe拓扑,根复合体(通常集成在CPU中)作为系统的中心,通过交换机连接多个端点设备,如NVMe SSD、GPU和网卡。每个链路都是独立的。)

分层模型

PCIe架构遵循一个标准的分层通信模型,这与网络协议栈(如TCP/IP)非常相似。这种分层设计使得上下层之间可以独立演进,也便于理解和实现。

图2-2:PCIe分层通信模型

+-------------------------------------------------------+

| 软件/驱动程序层 |

| (产生读/写请求,配置空间访问) |

+-------------------------------------------------------+

|

+-------------------------------------------------------+

| 事务层 (Transaction Layer) |

| - 组装/解包TLP (事务层数据包) |

| - 流量控制 (Flow Control) |

| - 服务质量 (QoS) |

+-------------------------------------------------------+

|

+-------------------------------------------------------+

| 数据链路层 (Data Link Layer) |

| - 组装/解包DLLP (数据链路层数据包) |

| - 链路管理和ACK/NAK错误重试 |

+-------------------------------------------------------+

|

+-------------------------------------------------------+

| 物理层 (Physical Layer) |

| - 组装/解包PLP (物理层数据包) |

| - 8b/10b编码,扰码 |

| - 串行化/解串行化 (SerDes) |

| - 电气信号,链路训练 |

+-------------------------------------------------------+

(图例说明: 展示了PCIe的三层模型:事务层、数据链路层和物理层。数据包从上至下封装,从下至上解封装。)

数据包类型

数据在PCIe各层之间以数据包的形式传递:

TLP:在事务层产生,是承载实际读写数据和配置信息的核心数据包。NVMe命令和数据都通过TLP传输。

DLLP:在数据链路层产生,用于链路管理,如确认(ACK)、非确认(NAK)和流量控制信息。

PLP:在物理层产生,用于帧同步和链路训练。

【通俗比喻二:邮政系统】

将PCIe通信比作一个高效的邮政系统:

TLP 就是你寄送的信件或包裹本身,里面装着重要的内容(NVMe命令或数据)。

DLLP 就像是挂号信的回执,用于确认对方是否收到,如果没收到就重发。

物理层 就是邮政运输网络(公路、铁路、飞机),负责把信件从一个地方 physically 运到另一个地方。

交换机 就是邮件分拣中心,根据地址将信件路由到正确的目的地。

2.2 PCIe配置空间:如何被发现与识别?

当一个PCIe设备(如NVMe SSD)插入系统时,操作系统需要一种方式来发现它、识别它是什么设备、并对其进行配置。这就是PCIe配置空间 的职责。

每个PCIe功能(一个物理设备可能包含多个功能)都有一个独立的配置空间,它是一个大小为4KB的寄存器集合。其开头64字节是标准化的Header,对于NVMe这样的Endpoint设备,通常是Type 0 Header。

图2-3:PCIe配置空间Type 0 Header示意图

+----------------------+-----------------------------------+ | 寄存器偏移 | 说明 | +----------------------+-----------------------------------+ | 0x00 - 0x01 | Vendor ID (设备厂商ID) | | 0x02 - 0x03 | Device ID (设备ID) | | 0x08 - 0x08 | Revision ID (修订版本ID) | | 0x09 - 0x0B | Class Code (类代码) | | 0x0C - 0x0D | Subsystem Vendor ID | | 0x0E - 0x0F | Subsystem Device ID | | 0x10 - 0x27 | Base Address Registers (BARs) | | ... | ... (其他配置寄存器) | +----------------------+-----------------------------------+

(图例说明: 展示了PCIe配置空间头部关键寄存器的布局。)

关键寄存器解读:

Vendor ID & Device ID:唯一标识设备的制造商和具体型号。

Class Code:这是一个至关重要的字段。对于NVMe设备,它的值为 0x010802。这个值告诉操作系统:“我是一个遵循NVM Express规范的存储控制器”。

Base Address Registers:这是配置过程的核心。系统软件通过向BAR写入全1再回读,探测设备需要多大的内存地址空间。然后,操作系统会分配一段物理内存地址范围,并将其写入BAR。此后,CPU就可以通过访问这段内存地址来与NVMe设备的寄存器进行通信,包括访问NVMe的Doorbell寄存器。

【实践案例一:NVMe设备的发现与枚举】

系统上电后,BIOS/UEFI或操作系统遍历PCIe总线。

读取每个设备的配置空间,检查Vendor ID和Device ID。

当读到Class Code为0x010802时,系统知道这是一个NVMe控制器。

系统配置该设备的BAR,为其分配内存映射I/O空间。

系统加载对应的NVMe驱动程序,驱动程序通过BAR映射的地址开始与控制器通信,执行初始化序列。

2.3 PCIe数据传输机制:TLP、DLLP与流控

TLP详解

TLP是承载NVMe命令和数据的载体。一个TLP包主要包括:

Header:3或4个双字(DW),包含地址、事务类型(Mem Read/Write, Cfg Read/Write等)、数据长度、流量类别等。

Data Payload:可选,对于写事务,它包含要写入的数据;对于读完成事务,它包含读回的数据。

ECRC:可选的端到端循环冗余校验码。

NVMe控制器与主机驱动程序之间的通信,绝大部分是通过内存写事务TLP(用于更新Doorbell寄存器)和内存读/写事务TLP(用于在主机内存和SSD之间传输命令、完成项和数据)完成的。

流量控制

为了避免接收端缓冲区溢出导致数据丢失,PCIe实现了基于信用的(Credit-Based)流量控制机制。每个通信方向(发送和接收)对于每种类型的TLP(如Posted, Non-Posted)都有独立的信用池。

接收方会通过DLLP告知发送方自己当前的信用值(即可用的缓冲区大小)。

发送方只有在拥有足够信用时才会发送TLP,每发送一个包就消耗相应信用。

接收方处理完数据后,会通过DLLP更新信用,允许发送方继续发送。

这种机制保证了数据传输的可靠性,无需高层协议介入。

2.4 MSI/MSI-X中断机制:高性能中断的保障

当NVMe控制器完成一个命令后,它需要通知主机驱动程序。这个通知机制就是中断。

传统PCI中断:使用边带信号(INTx),共享且需要轮询识别中断源,延迟高且效率低。

MSI:允许设备通过发起一个内存写事务TLP 到特定的主机内存地址来传递中断消息。这是一个“带内”信号,更快更可靠。

MSI-X:是MSI的增强版,它支持多个独立的中断向量 和独立的目标地址。

表2-1:MSI与MSI-X对比

| 特性 | MSI | MSI-X |

|---|---|---|

| 中断向量数量 | 最多32个 | 最多2048个 |

| 向量掩码 | 有 | 无(每个向量独立) |

| 地址/数据 | 所有向量共享同一组地址/数据 | 每个向量有独立的地址和数据 |

| 灵活性 | 低 | 高 |

MSI-X对NVMe性能的关键作用:

NVMe规范强烈推荐使用MSI-X。它允许为每个I/O队列分配一个独立的中断向量。这意味着,当某个CPU核心处理的队列完成命令时,中断可以被直接发送到该核心,实现了中断的亲和性,避免了核心间中断(IPI)的开销,极大地提升了多核环境下的并行处理效率。

2.5 NVMe如何构建在PCIe之上:一个高效的“乘客”

现在,我们可以将前面所有的知识点串联起来,描绘出NVMe如何优雅地构建在PCIe这座高速桥梁之上。

发现与连接:系统通过PCIe配置空间发现NVMe控制器,并通过BAR为其分配“通信窗口”。

命令提交:驱动程序将命令放入主机内存中的SQ,然后通过一个内存写事务TLP(写入NVMe控制器的Doorbell寄存器)来通知控制器。

命令执行:控制器获取命令,如果需要传输数据,则发起DMA操作,通过内存读TLP(对于读命令)或内存写TLP(对于写命令)在主机内存和控制器缓冲区之间搬运数据。

命令完成:控制器将完成状态写入主机内存中的CQ,然后通过MSI-X中断TLP 通知驱动程序。

完成确认:驱动程序处理完成项,并通过内存写TLP(写入完成队列Doorbell)告知控制器该CQ条目已被处理。

【通俗比喻三:高效的物流中心】

PCIe总线:是整个城市的高速公路网络和物流标准。

TLP:是高速公路上跑的标准集装箱卡车。

NVMe协议:是建立在物流网络之上的一个超高效的物流公司运营手册。

Doorbell寄存器:是物流中心门口的“有货待取”按钮,按一下就能通知里面的人。

MSI-X中断:是送货完成后,快递员直接给收货人打的专属电话,而不是去小区门卫室用大喇叭喊。

NVMe充分利用了PCIe提供的所有高性能特性:点对点拓扑、分层协议、高效的TLP数据传输、以及灵活的MSI-X中断。它没有在PCIe之上增加任何不必要的抽象层,而是直接、紧密地与硬件交互,这正是其低延迟和高效率的终极奥秘。

第三章:NVMe 1.4c规范精解(上) – 命令与队列

3.1 基本概念:控制器、命名空间、队列

在深入NVMe的动态操作之前,必须首先理解其静态的组成要素。这些概念构成了NVMe协议的逻辑模型。

图3-1:NVMe逻辑架构组成

+--------------------------------------------------+

| 主机系统 (Host) |

| +--------------------------------------------+ |

| | 应用程序 | |

| +--------------------+-----------------------+ |

| | (文件系统/块层) |

| +--------------------v-----------------------+ |

| | NVMe 驱动程序 | |

| +---------+------------------+---------------+ |

| | | |

| +-------v-------+ +------v--------+ |

| | 提交队列 SQ | | 完成队列 CQ | |

| | (内存中) | | (内存中) | |

| +---------------+ +---------------+ |

+--------------------------------------------------+

| (PCIe TLP) | (PCIe TLP)

+-----------v-----------------------v---------------+

| NVMe 控制器 |

| +--------------------------------------------+ |

| | 控制器逻辑 & 处理引擎 | |

| +--------------------------------------------+ |

| | 闪存转换层 FTL | |

| +--------------------------------------------+ |

| | NAND 接口介质 | |

| +--------------------------------------------+ |

+--------------------------------------------------+

| 命名空间 (Namespace) |

| (逻辑块地址 LBA 的连续集合) |

+--------------------------------------------------+

(图例说明: 展示了主机软件栈、主机内存中的队列、PCIe总线、NVMe控制器以及底层的命名空间之间的逻辑关系。)

1. NVMe控制器

这是NVMe SSD的“大脑”,是一个PCIe功能单元。它负责:

解析和执行来自主机的NVMe命令。

管理主机内存中的I/O队列。

通过PCIe接口与主机通信。

执行闪存转换层功能,将逻辑地址映射到物理闪存位置。

一个物理SSD上通常有一个控制器,但规范也支持多个控制器。

2. 命名空间

命名空间是NVMe控制器提供的非易失性存储的逻辑划分。可以将其理解为一个虚拟硬盘。

每个命名空间由一段连续的逻辑块地址 范围组成。

一个控制器可以附加一个或多个命名空间。

不同的命名空间可以有不同的格式化属性(如LBA大小、端到端数据保护设置)。

这种抽象允许灵活的数据管理,例如为不同应用或用户隔离存储空间。

3. 队列

队列是NVMe实现其高性能的核心机制。它是一种在生产者和消费者之间传递工作项的数据结构。

提交队列:生产者(主机驱动程序)将需要执行的命令放入SQ。

完成队列:消费者(NVMe控制器)在执行完命令后,将完成状态放入CQ。

NVMe严格遵循生产者-消费者模型,并且SQ和CQ是成对出现的。

【通俗比喻一:餐厅厨房】

NVMe控制器 = 整个餐厅的后厨团队。

命名空间 = 后厨管理的不同食材储藏区(如冷藏库、干货库)。

提交队列(SQ) = 前台服务员提交给后厨的点菜单。

完成队列(CQ) = 后厨做完菜后,放在出菜口的铃铛和订单号,通知服务员上菜。

3.2 提交队列与完成队列:生产者-消费者模型的完美体现

让我们深入队列的细节。SQ和CQ都驻留在主机内存中,由主机分配和管理,但其内容由主机和控制器共同访问。

队列工作原理:

命令提交:

驱动程序准备好命令后,将其放入下一个空闲的SQ条目。

驱动程序更新其内部的SQ尾指针。

驱动程序通过一次PCIe内存写事务(写入控制器的门铃寄存器),告知控制器SQ中有新的命令待处理。

命令获取与执行:

控制器监测到门铃寄存器更新后,从SQ中获取命令。

控制器执行命令(可能涉及DMA数据传输)。

命令执行完毕后,控制器创建一个完成队列条目。

完成通知:

控制器将CQE放入CQ。

控制器更新其内部的CQ头指针。

控制器可能产生一个MSI-X中断,通知主机有命令已完成。

完成处理:

驱动程序的中断服务例程检查CQ。

驱动程序处理CQE。

驱动程序通过一次PCIe内存写事务(写入控制器的完成队列门铃寄存器),告知控制器该CQE已被消费,控制器可以回收该条目。

图3-2:队列与门铃寄存器工作流程

+---------+ +-----------------+ +---------+

| 主机 | | 主机内存 | | NVMe |

| 驱动 | | | | 控制器 |

+---------+ +-----------------+ +---------+

| | |

| 1. 填充SQ条目 | |

|------------------->| |

| | |

| 2. 更新内部尾指针 | |

|--+ | |

| | | |

| | 3. 写SQ门铃 | |

| |---------------------------------------->|

| | |

| | 4. 从SQ取命令 |

| |<---------------------|

| | |

| | 5. 执行命令(DMA) |

| |<-------------------->|

| | |

| | 6. 填充CQ条目 |

| |<---------------------|

| | |

| | 7. 产生MSI-X中断 |

|<-------------------------------------------|

| | |

| 8. 处理CQ条目 | |

|------------------->| |

| | |

| 9. 写CQ门铃 | |

|------------------------------------------->|

| | |

(图例说明: 该序列图清晰地展示了命令从提交到完成的完整生命周期中,主机驱动、主机内存和NVMe控制器三者的交互。)

3.3 门铃寄存器:高效的硬件信令机制

门铃寄存器是NVMe协议中一个简单而高效的设计。它们是映射到控制器BAR空间的一组简单的32位写操作寄存器。

每个SQ和CQ都有自己对应的门铃寄存器对。

写入值:驱动程序写入的是其内部的尾指针(对于SQ)或头指针(对于CQ) 的值。

作用:这次写入操作本身,就是对控制器的一个信号。控制器通过比较新旧指针值,就能知道有多少个新的命令需要处理,或者有多少个CQE条目可以被回收。

关键点:

门铃寄存器写入是幂等的,多次写入相同的值不会改变行为。

它避免了复杂的握手机制,通过一次简单的内存写操作就完成了信令,极大降低了延迟。

3.4 Admin队列与I/O队列:管理平面与数据平面的分离

NVMe对队列进行了逻辑上的划分,实现了控制流与数据流的分离。

1. Admin提交队列和Admin完成队列

这是唯一在控制器初始化时必须存在的队列对。

用于执行所有管理和控制命令,例如:

创建/删除I/O队列。

附加/分离命名空间。

获取日志页面。

固件激活。

控制器复位。

通常只有一对,深度较浅。

2. I/O提交队列和I/O完成队列

用于执行所有数据操作命令,例如:Read, Write, Flush。

数量可以非常多(最多64K-1对)。

主机软件可以根据需要动态创建和删除它们。

这种设计允许不同的应用程序或CPU核心使用专用的队列对,实现极致的并行性和服务质量隔离。

表3-1:Admin队列与I/O队列对比

| 特性 | Admin 队列 | I/O 队列 |

|---|---|---|

| 队列ID | 固定为0 | 动态分配 (1 to 65535) |

| 用途 | 管理控制器和命名空间 | 数据传输 (Read/Write) |

| 命令类型 | Identify, Create IOQ, etc. | Read, Write, Flush, etc. |

| 必需数量 | 1对 | 0到65535对 |

| 典型深度 | 32-64 | 64-1024+ |

3.5 NVMe命令格式详解:PRP与SGL两种数据指针

每个提交队列条目都是一个固定大小的数据结构,包含命令的所有信息。一个NVMe命令通常由几个双字组成,其通用格式如下:

图3-3:NVMe命令通用格式(以64字节为例)

+---------------+---------------+---------------+---------------+ | DW0 | DW1 | DW2 | DW3 | |---------------+-------+-------+---------------+---------------+ | Opcode | FUSE | 保留 | 命令标识符 CID | +---------------+---------------+---------------+---------------+ | 命名空间ID NSID | 其他命令特定字段... | +-------------------------------+-------------------------------+ | 元数据指针 (MPTR) | +---------------------------------------------------------------+ | 数据指针 (DPTR) | | (PRP1/SGL1) | +---------------------------------------------------------------+ | 数据指针 (DPTR) | | (PRP2/SGL2) | +---------------------------------------------------------------+ | 命令特定字段 DWORD 10-15 | +---------------------------------------------------------------+

(图例说明: 展示了NVMe命令的基本布局,关键字段包括操作码、命名空间ID和数据指针。)

关键字段:

Opcode:指定要执行的操作(如01h为Flush, 02h为Write, 05h为Read)。

NSID:指定命令操作的目标命名空间。

CID:命令标识符,用于在CQ中匹配完成状态。

数据指针:这是命令格式中最复杂也最关键的部分,它告诉控制器数据在主机内存中的位置。NVMe支持两种机制:PRP和SGL。

PRP

PRP是一种基于物理内存页的寻址方式。

PRP1:指向数据缓冲区的第一个物理内存页。如果数据只在一个物理页内,PRP2无效。

PRP2:可以是一个指向第二个物理内存页的指针,或者是一个指向PRP列表的指针。PRP列表是一个物理页地址的数组,用于描述分散在多个不连续物理页中的数据缓冲区。

PRP的优点是结构简单,控制器处理开销小。缺点是要求数据缓冲区在物理内存中是页对齐的,并且对于极度分散的缓冲区,需要创建PRP列表,增加了驱动程序的复杂性。

SGL

SGL是一种更现代、更灵活的数据描述机制。它使用描述符来指向一段数据缓冲区,每个描述符包含:

地址:数据缓冲区的起始地址(可以是物理或IOVA地址)。

长度:该缓冲区的长度。

类型:标识这是数据段、指向下一个SGL的指针,还是链的结束。

SGL的优点:

灵活性:可以高效地描述任意长度、任意分散的数据缓冲区,无需页对齐。

效率:对于分散-聚集I/O(如网络数据包),SGL比PRP高效得多。

表3-2:PRP与SGL数据指针对比

| 特性 | PRP | SGL |

|---|---|---|

| 基本原理 | 基于物理内存页 | 基于数据段描述符链表 |

| 内存对齐要求 | 必须页对齐 | 无强制对齐要求 |

| 描述分散缓冲区能力 | 尚可,需要PRP列表 | 优秀,原生支持 |

| 控制器处理复杂度 | 较低 | 稍高(需要解析链表) |

| NVMe 1.0支持 | 是 | 否(1.1引入) |

| 行业趋势 | 传统,稳定 | 现代,推荐,更灵活 |

【实践总结】:现代NVMe驱动和控制器普遍倾向于使用SGL,因为它能更好地适应现代操作系统和应用的内存使用模式。

3.6 命令执行的全流程:从驱动到硬件的旅程

让我们以一个 NVMe Write命令 为例,串联起本章的所有概念,描绘其完整的执行路径:

驱动准备:

驱动程序在主机内存中准备好要写入的数据。

驱动程序获取一个空闲的SQ条目(例如在SQ 3)。

填充命令DWORD:Opcode=01h (Write), NSID=1, CID=0xAB。

根据数据缓冲区的位置,填充SGL或PRP数据指针。

驱动程序更新其内部的SQ尾指针为4。

通知控制器:

驱动程序执行一次内存写操作,向SQ 3的门铃寄存器写入值4。

控制器获取:

控制器通过PCIe接收到门铃写入,知道SQ 3中有新命令。

控制器通过DMA从主机内存的SQ 3中读取命令条目。

数据处理:

控制器解析SGL/PRP,了解到数据在主机内存中的位置。

控制器发起DMA读操作,通过PCIe内存读TLP,将数据从主机内存传输到控制器的内部缓冲区。

执行与完成:

控制器将数据写入NAND闪存。

操作完成后,控制器在CQ中创建一个完成条目,其中包含状态(成功/失败)和匹配的CID (0xAB)。

控制器产生一个MSI-X中断通知主机。

驱动清理:

驱动程序的中断服务例程检查CQ,发现CID为0xAB的命令已完成。

驱动程序处理状态,标记SQ条目3为空闲。

驱动程序向CQ的门铃寄存器写入新的头指针,告知控制器CQ条目已被消费。

至此,一个完整的NVMe Write命令生命周期结束。这个过程充分展示了NVMe协议的精简与高效。

3.7 多队列与多核心扩展性:为何NVMe能充分利用CPU?

在第一章我们已经提到,NVMe通过多队列设计解决了AHCI的单队列瓶颈。现在让我们深入探讨这一机制如何在实际系统中发挥威力。

队列分配策略

在现代操作系统中,NVMe驱动程序通常采用以下策略来分配队列:

每CPU核心队列:为每个CPU核心创建专用的I/O队列对。这样,运行在特定核心上的应用程序发起的I/O请求只会进入该核心的队列,避免了核心间的锁竞争和缓存同步开销。

每进程/线程队列:在更细粒度上,可以为关键进程或线程分配专用队列,实现更好的隔离性和服务质量保证。

图3-4:多队列在多核系统中的工作模式

+--------------------------------------------------+

| 多核CPU系统 |

| +--------+ +--------+ +--------+ +--------+ |

| | 核心 0 | | 核心 1 | | 核心 2 | | 核心 3 | |

| +--------+ +--------+ +--------+ +--------+ |

| | | | | |

| +---v---+ +---v---+ +---v---+ +---v---+ |

| | SQ/CQ | | SQ/CQ | | SQ/CQ | | SQ/CQ | |

| | 1 | | 2 | | 3 | | 4 | |

| +---+---+ +---+---+ +---+---+ +---+---+ |

| | | | | |

+------|-----------|-----------|-----------|-------+

| | | |

+-----------+-----------+-----------+

|

+-------v-------+ PCIe总线

| NVMe控制器 |

| +-----------+ |

| | 队列仲裁 | |

| | 与调度 | |

| +-----------+ |

+---------------+

(图例说明: 展示了四个CPU核心各自拥有专用的SQ/CQ对,这些队列通过PCIe总线被NVMe控制器并发处理。)

性能优势体现

线性扩展:随着CPU核心数量的增加,NVMe设备的IOPS性能几乎可以线性增长,而基于AHCI的设备则会很快达到单队列的瓶颈。

降低延迟:避免了全局锁竞争和核心间中断,使得命令从提交到完成的路径更短,延迟更低且更稳定。

【实践案例一:数据库性能测试】

在一个24核心的服务器上测试数据库事务处理:

使用AHCI SSD时,IOPS在8核心后基本不再增长,CPU利用率显示大量核心处于空闲或等待状态。

使用NVMe SSD时,IOPS随核心数增加持续上升至20核心以上,所有CPU核心都得到有效利用,总吞吐量提升超过300%。

3.8 端到端数据保护:DIF/DIX详解

在数据存储路径中,从应用程序到存储介质,数据可能经过多个组件(主机内存、PCIe总线、控制器缓存、NAND闪存),每个环节都有发生静默数据损坏的风险。NVMe通过端到端数据保护机制来防范这种风险。

保护信息格式

NVMe支持两种主要的保护信息格式:

DIF:保护信息与每512字节数据块一起存储,通常为8字节,包含CRC校验和和其他保护字段。

DIX:保护信息与用户数据分开存储,在传输过程中与数据一起传递,但最终存储在独立的区域。

图3-5:端到端数据保护工作原理

+-------------------+ +-------------------+ +-------------------+

| 主机应用程序 | | NVMe控制器 | | NAND闪存 |

+-------------------+ +-------------------+ +-------------------+

| | |

| 用户数据 + 保护信息 | |

|------------------------>| |

| | 验证保护信息 |

| |--+ |

| | | 如果校验失败,返回错误|

| |<-+ |

| | |

| | 用户数据 + 保护信息 |

| |------------------------>|

| | |

(图例说明: 展示了数据从主机传输到控制器的过程中,保护信息随数据一起传递并被验证。)

保护类型

NVMe定义了多种保护类型,可以在命名空间格式化时配置:

Type 1:保护信息从主机传递到介质,控制器必须验证和保护数据完整性。

Type 2:保护信息由控制器生成并验证,主机不参与。

Type 3:保护信息由主机生成,控制器不验证但将其存储到介质。

【实践案例二:企业级数据完整性】

在金融或医疗系统中,确保数据从写入到读取的完整一致性至关重要。通过配置NVMe端到端数据保护,可以:

检测到内存、总线或控制器内部的数据损坏。

在数据损坏发生时立即返回错误,而不是返回损坏的数据。

与上层应用的数据完整性机制(如数据库的checksum)形成双重保护。

3.9 命名空间管理、附件与分区

命名空间管理

NVMe 1.4引入了更灵活的命名空间管理模型,允许动态创建、删除和调整命名空间大小。

ANAGRPID:附件命名空间组ID,用于将多个命名空间分组管理。

NSFEAT:命名空间特性,定义了命名空间支持的特定功能。

命名空间附件

这是一个重要的新特性,允许多个控制器共享访问同一个命名空间。这为实现多路径I/O和高可用性提供了基础。

一个命名空间可以同时附加到多个控制器。

当某个控制器发生故障时,I/O可以通过其他控制器继续访问该命名空间。

需要主机软件和控制器固件的协同支持。

分区命名空间

ZNS是NVMe 2.0规范中的重要特性,但在1.4中已奠定基础。它将命名空间划分为多个区域,每个区域必须顺序写入,但可以随机读取。

优势:大幅减少FTL的映射表大小,降低写放大,提升SSD寿命和性能一致性。

应用场景:非常适合大数据、流式写入和日志结构的数据存储模式。

表3-3:传统命名空间与分区命名空间对比

| 特性 | 传统命名空间 | 分区命名空间 (ZNS) |

|---|---|---|

| 写入模式 | 任意LBA随机写入 | 必须在区域内顺序写入 |

| FTL映射表 | 巨大,需要缓存所有LBA | 很小,只需管理区域映射 |

| 写放大 | 较高 | 极低 |

| 性能一致性 | 受垃圾回收影响大 | 非常稳定 |

| 适用场景 | 通用工作负载 | 大数据、日志、对象存储 |

3.10 持久化日志区域与异常恢复

为了应对意外断电等异常情况,NVMe设计了持久化日志区域机制。

持久化事件日志

控制器将关键事件(如硬件错误、温度告警、SMART数据)记录到非易失性日志区域。

系统重启后,驱动程序可以读取这些日志,分析异常原因。

支持多种日志页面:错误信息、健康状态、固件日志等。

异常恢复流程

当系统从异常断电恢复时:

控制器上电后进入恢复状态。

驱动程序读取控制器的状态寄存器,了解恢复进度。

驱动程序访问持久化事件日志,了解断电时的系统状态。

根据日志信息,重建队列状态,恢复未完成的命令。

如有必要,重新初始化控制器并重建所有I/O队列。

3.11 Sanitize、Firmware管理等高阶功能

Sanitize操作

这是企业级SSD的关键安全特性,用于安全地、不可恢复地擦除所有用户数据。

Block Erase:块擦除,最快速但不一定最安全。

Overwrite:用特定模式覆盖所有用户数据区域。

Crypto Erase:删除加密密钥,使数据无法解密(要求SSD支持自加密)。

应用场景:设备退役、数据迁移前的安全清理。

固件管理

NVMe提供了标准的固件更新机制:

多个固件槽:控制器支持多个固件镜像槽位。

原子更新:通过单个固件下载命令传输整个固件镜像。

激活调度:可以立即激活或计划在下次重启时激活新固件。

回滚保护:确保在固件更新失败时能回退到已知正常版本。

其他高级特性

虚拟化支持:通过SR-IOV技术,单个物理NVMe设备可以呈现为多个虚拟功能,直接分配给不同虚拟机。

温度阈值管理:监控控制器温度,在过热时采取限速或关机等保护措施。

预测性维护:通过SMART日志提供设备健康状态预测,提前预警潜在故障。

3.12 NVMe over Fabrics初探

虽然NVMe-oF是更高级的主题,但在基础协议中理解其核心概念十分重要。

基本架构

NVMe over Fabricks将NVMe协议扩展到网络结构上,核心变化是:

传输队列:取代了PCIe的门铃寄存器机制,通过网络消息实现队列同步。

胶囊:将NVMe命令、数据和完成状态封装在网络数据包中传输。

主要传输类型

NVMe over RDMA:利用RoCE、iWARP或InfiniBand实现远程直接内存访问,性能最佳。

NVMe over TCP:基于标准以太网TCP/IP,部署最方便,已成为主流。

NVMe over Fibre Channel:利用FC网络基础设施。

图3-6:NVMe与NVMe over Fabrics协议栈对比

+----------------+ +-----------------------+ | 本地NVMe | | NVMe over Fabrics | +----------------+ +-----------------------+ | 应用程序 | | 应用程序 | +----------------+ +-----------------------+ | NVMe驱动 | | NVMe-oF驱动 | +----------------+ +-----------------------+ | PCIe | | RDMA/TCP/FC栈 | +----------------+ +-----------------------+ | 物理层 | | 网络物理层 | +----------------+ +-----------------------+

(图例说明: 对比了本地NVMe和NVMe over Fabrics的协议栈,可以看到NVMe-oF使用网络协议栈替代了PCIe栈。)

核心价值

解耦存储:计算和存储可以独立扩展。

资源共享:多个服务器可以共享高性能存储池。

延长距离:突破机箱内PCIe总线的距离限制。

本章总结

第三章完整地介绍了NVMe 1.4c协议的核心机制和高级特性。从基础的队列模型、命令格式,到高级的多队列并行性、端到端数据保护、命名空间管理,再到Sanitize和固件管理等企业级功能,NVMe协议展现了一个为现代存储需求精心设计的完整生态系统。

理解这些协议细节对于芯片架构师至关重要,因为接下来的章节将深入探讨如何将这些协议特性转化为实际的硬件设计。

第四章:NVMe协议扩展与系统集成

4.1 多路径I/O与命名空间共享

在现代数据中心和高可用系统中,避免单点故障至关重要。NVMe通过多路径I/O和命名空间共享提供了存储高可用性的基础。

多路径I/O架构

多路径I/O允许主机通过多个独立的控制器访问同一个命名空间,当某个路径发生故障时,I/O可以自动切换到其他可用路径。

图4-1:NVMe多路径I/O架构

+-----------------------+

| 主机系统 |

| +-----------------+ |

| | 多路径驱动 | |

| | (Multipath) | |

| +--------+--------+ |

| | |

| +--------+--------+ |

| | NVMe驱动 | |

| +--------+--------+ |

| | |

+-----------|-----------+

|

+-------v-------+ +-------v-------+

| NVMe控制器 | | NVMe控制器 |

| A | | B |

+-------+-------+ +-------+-------+

| |

+-------+-------+ +-------+-------+

| 命名空间1 | | 命名空间2 |

| (私有) | | (私有) |

+---------------+ +---------------+

| |

+-------+-----------------------+-------+

| 命名空间X |

| (共享命名空间) |

+---------------------------------------+

| NAND闪存阵列 |

+---------------------------------------+

(图例说明: 展示了两个NVMe控制器共享访问同一个命名空间X,主机通过多路径驱动可以同时看到两条路径。)

实现机制

命名空间附件:通过

Namespace Attachment

路径发现:主机通过

Identify Controller

Identify Namespace

路径故障切换:当某条路径发生超时或错误时,多路径驱动自动将后续I/O导向其他健康路径。

负载均衡:高级多路径驱动可以在多条路径间均衡I/O负载,提高整体性能。

【实践案例一:数据库高可用架构】

在一个关键业务数据库系统中:

配置两个NVMe控制器共享访问同一组命名空间。

数据库通过多路径驱动同时看到两条存储路径。

正常情况下,读操作在两个控制器间负载均衡。

当控制器A因固件更新或故障离线时,所有I/O自动切换到控制器B,实现无缝故障转移。

4.2 虚拟化支持:SR-IOV与MR-IOV

虚拟化环境中,NVMe设备需要高效地分配给多个虚拟机。NVMe通过SR-IOV和MR-IOV技术提供近乎原生性能的虚拟化支持。

SR-IOV架构

SR-IOV允许单个物理NVMe设备呈现为多个虚拟功能,每个VF可以直接分配给一个虚拟机,绕过Hypervisor的软件模拟层。

图4-2:NVMe SR-IOV架构

+--------------------------------------------------+ | 物理主机 | | +--------------+ +--------------+ | | | 虚拟机A | | 虚拟机B | | | | | | | | | | +----------+ | | +----------+ | | | | | NVMe驱动 | | | | NVMe驱动 | | | | | +----------+ | | +----------+ | | | +------|-------+ +------|-------+ | | | | | | +------v-------------------v-------------------+ | | | NVMe SR-IOV 设备 | | | | +-------------+ +-------------+ | | | | | 虚拟功能 | | 虚拟功能 | | | | | | (VF) | | (VF) | | | | | +-------------+ +-------------+ | | | | | | | | +-------------+ | | | | | 物理功能 | | | | | | (PF) | | | | | +-------------+ | | | +----------------------------------------------+ | +--------------------------------------------------+

(图例说明: 展示了单个物理NVMe设备通过SR-IOV技术呈现为多个虚拟功能,每个VF可以直接被虚拟机使用。)

关键特性

性能隔离:每个VF有独立的队列资源和带宽保障。

直接I/O:虚拟机驱动直接与VF通信,避免Hypervisor开销。

灵活配置:PF由Hypervisor管理,用于设备配置和监控;VF分配给虚拟机用于数据I/O。

扩展性:单个NVMe设备可以支持数十个甚至数百个VF。

MR-IOV进阶

MR-IOV是SR-IOV的扩展,允许跨多个物理设备的资源池化和统一管理,为大规模虚拟化环境提供更高级的灵活性。

4.3 电源管理:自动功耗状态转换

随着数据中心规模扩大和能效要求提高,NVMe的电源管理特性变得愈发重要。

功耗状态

NVMe定义了多个功耗状态,从全功率运行到深度睡眠:

表4-1:NVMe功耗状态概述

| 状态 | 描述 | 进入/退出延迟 | 典型功耗 | 适用场景 |

|---|---|---|---|---|

| PS0 | 活动状态 | – | 100% | 活跃I/O处理 |

| PS1 | 低功耗空闲 | 微秒级 | ~50% | 短暂空闲期 |

| PS2 | 中等功耗 | 几十微秒 | ~30% | 中等空闲 |

| PS3 | 深度睡眠 | 毫秒级 | ~10% | 长时间空闲 |

| PS4 | 设备睡眠 | 数十毫秒 | <5% | 系统待机 |

自动状态转换

NVMe控制器可以根据工作负载自动在功耗状态间转换:

工作负载预测:基于I/O模式预测空闲期长度。

自适应调整:根据历史数据动态调整状态转换阈值。

QoS保障:确保功耗管理不影响性能SLA。

【实践案例二:云服务提供商节能】

某大型云服务商通过优化NVMe电源管理:

在虚拟机空闲期,NVMe设备自动进入PS3状态。

当检测到I/O模式变化时,提前退出低功耗状态。

实现整体存储功耗降低35%,同时保证99.9%的I/O延迟SLA。

4.4 温度管理与热节流

高性能NVMe设备在工作时会产生大量热量,有效的温度管理对设备寿命和稳定性至关重要。

温度监控

复合温度传感器:监控控制器芯片温度。

NAND温度传感器:监控闪存芯片温度(通常耐温性较差)。

环境温度传感器:监控设备周围环境温度。

热节流策略

当温度超过阈值时,控制器自动启动保护机制:

图4-3:NVMe热节流工作流程

+----------------+ +----------------+ +----------------+

| 温度正常 | | 温度警告 | | 温度临界 |

| (< 70°C) | | (70-85°C) | | (> 85°C) |

+----------------+ +----------------+ +----------------+

| | |

| 温度持续上升 | 温度持续上升 | 温度持续上升

|---------------------->|---------------------->|

| | |

| | 记录温度警告日志 | 记录温度临界日志

| | 可选:轻度性能限制 | 强制性能节流

| | | 可能:紧急关机

| | |

| 温度下降 | 温度下降 | 温度下降

|<----------------------|<----------------------|

(图例说明: 展示了NVMe设备随温度升高采取的不同级别的热管理措施。)

主动冷却集成

现代NVMe设备与系统冷却方案深度集成:

风扇控制:通过PWM信号调节冷却风扇转速。

功耗限制:动态限制设备最大功耗以减少热量产生。

工作负载调度:在多个设备间均衡负载,避免局部过热。

4.5 时间命名空间与确定性延迟

对于实时性要求极高的应用(如金融交易、工业自动化),NVMe引入了时间命名空间特性,提供确定性I/O延迟。

确定性延迟技术

预分配资源:为时间敏感型工作负载保留专用的队列和处理资源。

优先级调度:确保高优先级I/O在任何情况下都能获得即时服务。

延迟预测:基于设备内部状态提供准确的I/O完成时间预测。

应用场景

高频交易:确保订单在微秒级别内持久化。

实时数据分析:保证流处理管道的稳定吞吐量。

边缘计算:在资源受限环境中满足关键任务的延迟要求。

表4-2:标准命名空间与时间命名空间对比

| 特性 | 标准命名空间 | 时间命名空间 |

|---|---|---|

| 延迟特性 | 最佳努力 | 确定性上限 |

| 资源分配 | 共享 | 专用预留 |

| 适用工作负载 | 通用 | 实时敏感型 |

| 配置复杂度 | 简单 | 需要精细调优 |

4.6 NVMe与计算存储集成

计算存储是存储领域的新范式,将计算能力推向数据所在的位置。NVMe协议为计算存储提供了理想的载体。

计算存储架构

智能控制器:在NVMe控制器中集成专用处理单元(如FPGA、ASIC)。

近数据计算:在数据传输路径上执行计算任务,减少数据移动。

标准接口:通过NVMe命令集暴露计算能力。

计算存储用例

数据压缩/加密:在写入时透明压缩,读取时解压缩。

搜索过滤:在存储设备内直接执行数据查询,仅返回结果。

机器学习:在数据源头执行模型推理或特征提取。

视频处理:直接生成不同码率的视频流。

【实践案例三:智能视频分析】

一个城市安防系统:

摄像头视频流直接写入NVMe计算存储设备。

设备内置的AI处理器实时分析视频内容,检测异常事件。

仅将可疑片段的元数据和关键帧传输到中央服务器。

减少网络带宽消耗90%,提升分析响应速度5倍。

4.7 协议兼容性与多代支持

NVMe协议保持向前和向后兼容,确保生态系统的持续健康发展。

版本兼容策略

强制功能:每个NVMe版本定义必须实现的功能子集。

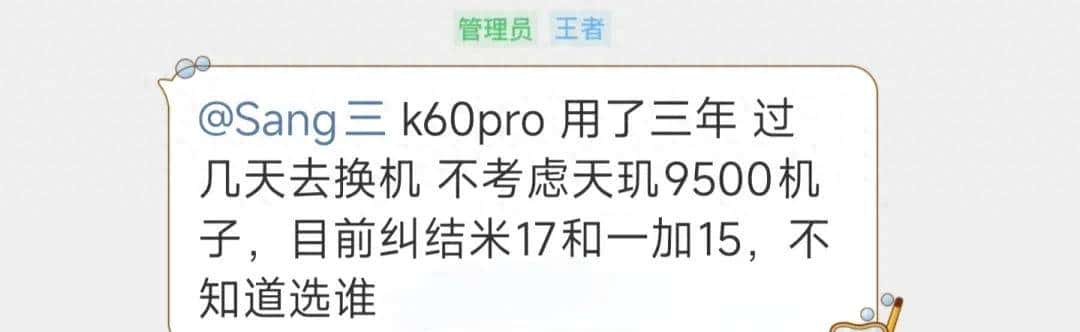

可选功能:通过

Identify Controller

渐进采用:新功能首先作为可选特性引入,后续版本可能变为强制。

多代设备管理

功能协商:主机与设备协商共同支持的功能集。

降级运行:新主机可以安全地与旧设备协作,仅使用共同支持的功能。

特性探测:驱动程序通过标准机制探测设备能力,动态启用相应优化。

生态系统影响

驱动统一:同一驱动版本支持多代NVMe设备。

管理简化:减少配置复杂性和维护成本。

投资保护:确保旧设备在新系统中继续有效工作。

本章总结

第四章深入探讨了NVMe协议在现代计算环境中的关键扩展功能。从确保高可用的多路径I/O,到提供极致虚拟化性能的SR-IOV;从精细的电源管理和温度控制,到满足实时性要求的时间命名空间;最后展望了代表未来方向的NVMe计算存储集成。

这些高级特性表明,NVMe已经从一个单纯的高速存储接口,演进成为支撑现代数据中心和各类专业应用的完整存储解决方案平台。理解这些扩展功能对于设计能够满足多样化需求的NVMe芯片至关重要。

相关文章